Simple CPU Instruction Set Design

It actually takes very little hardware to implement a simple CPU. Today in class we built a CPU with the very basics:

- An instruction fetch unit, which grabs the next instruction. The bits of the instruction are what activate different parts of the CPU circuit to make things happen. See the bits in various CPU instruction sets here

- A register file, from which operands are read, and results are written.

- An arithmetic unit, which performs operations on the operands.

There are a few key tricks used throughout these designs:

- In a CPU, we need some way to keep operating on the same values. In a circuit, this means feeding the output of the circuit back around to its own input, recycling the same values over and over.

- Most CPUs operate on values of more than one bit. Using a single bus to represent multiple bits with a single line dramatically simplifies the circuit schematic compared to the physically more realistic approach of drawing separate wires for each bit. Logisim calls this "Data Bits"; most other tools call it a "bus".

- A multiplexor selects one input line from a set of inputs, based on "select line". For example, an 8-in mux has a 3 bit select input, which is a binary code indicating which of the 8 inputs to select as the output. Multiplexors are used:

- In the register file, to select which register should provide input data for arithmetic. The register select lines are controlled by the input register portion of the instruction being executed.

- In the arithmetic unit, to pick the output of one arithmetic circuit from those listed. The arithmetic select lines are controlled by the opcode portion of the instruction.

Timing matters! In a real circuit timing is often the most important consideration for both performance and correctness. In the simulator, all the registers are edge-triggered. To avoid timing bugs, we fetch the next instruction on one edge of the clock, and write the results on the opposite edge of the clock, which prevents bugs where the register grabs a value as it changes. In a more complex design, we might need to keep a shift register to cycle between operating stages within a single instruction.

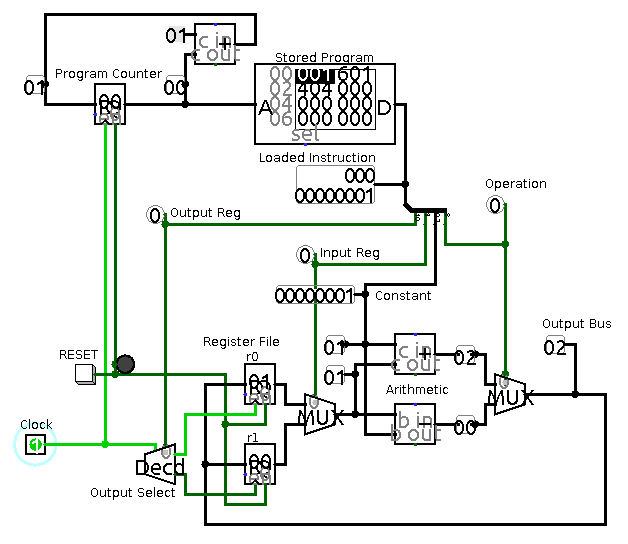

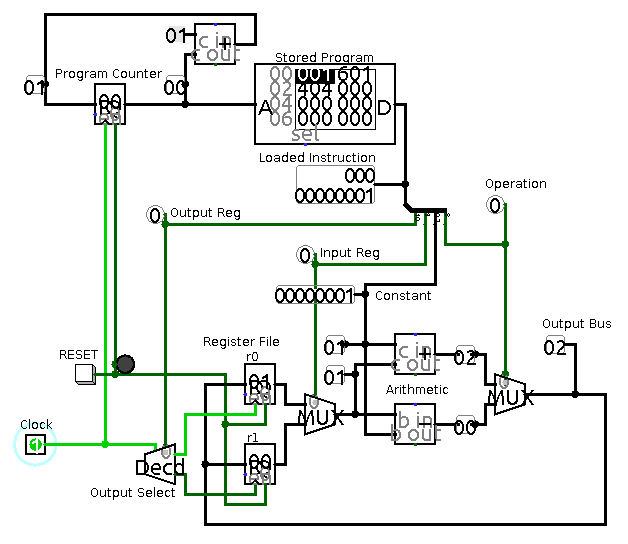

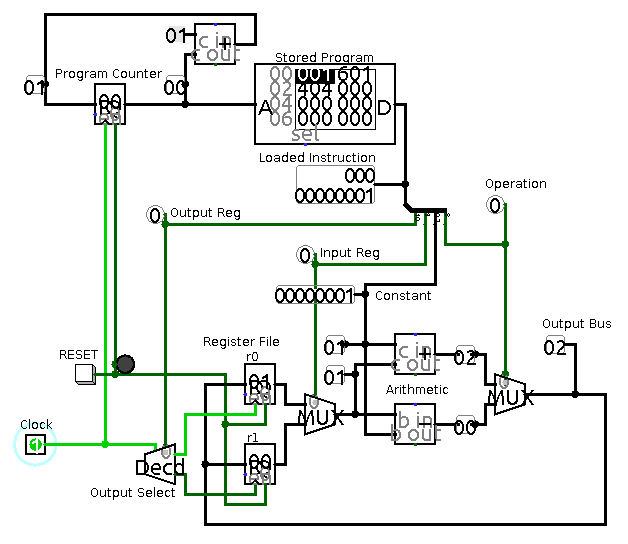

Here's the compact 11-bit instruction set CPU we built in class in 2018.

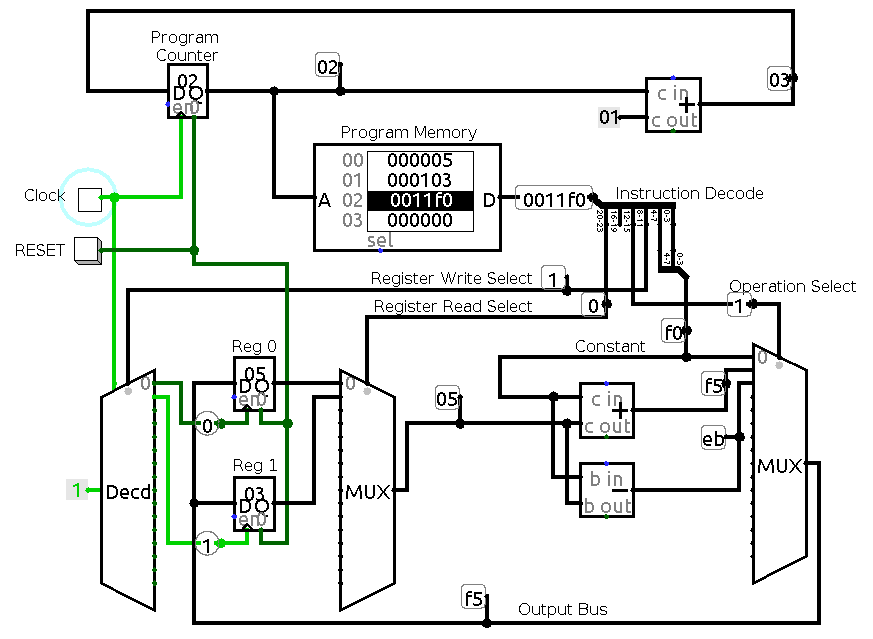

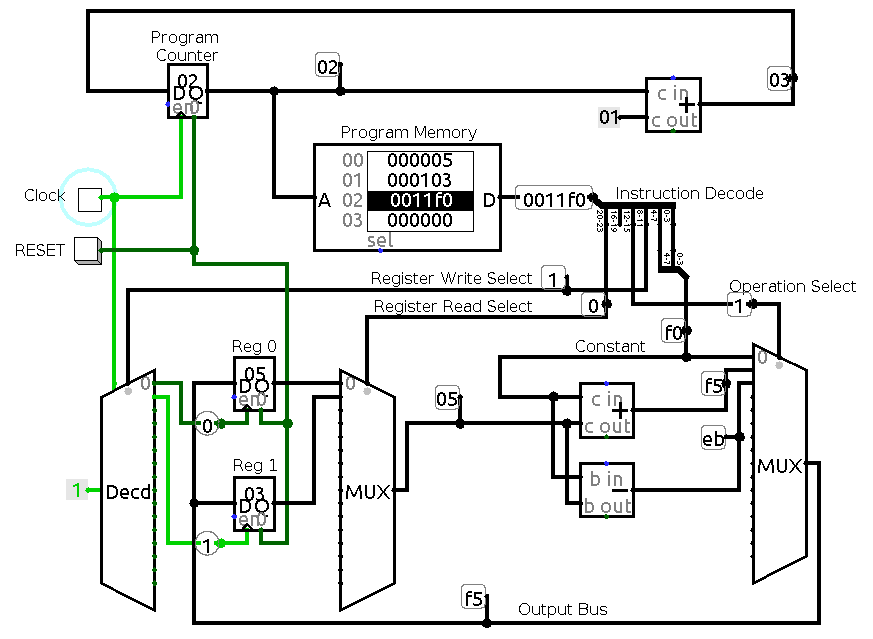

Here's the extensible 24-bit instruction set CPU we built in class in 2016.

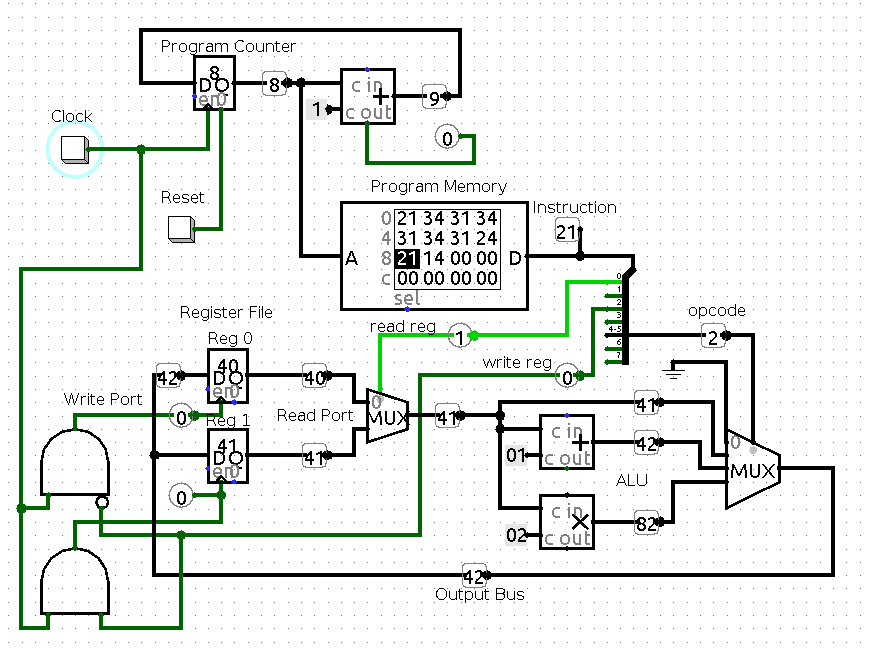

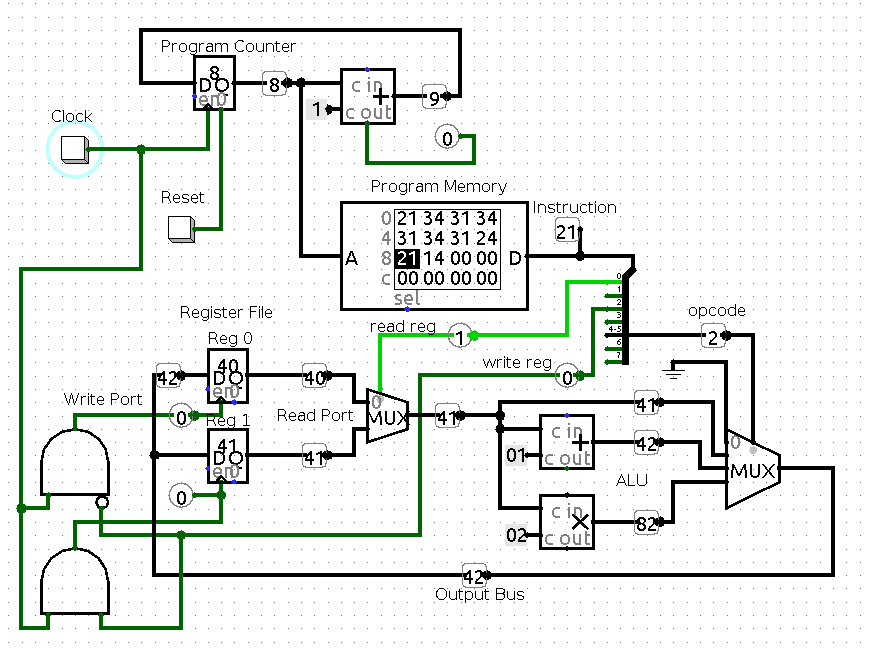

Here's an 8-bit instruction CPU we built in class in 2014. A few more examples are listed at my 2012 CPU design page.

CS 441 Lecture Note, Dr. Orion Lawlor, UAF Computer Science Department.